Документ подписан простой электронной подписью

Информация о владельце:

ФИО: Шебзухом ИНТИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАВОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ Должность: Директор ВЕДЕРАЛЬНОЕ ЧТОЕ УДАР СТВЕННОЕ АВТОНОМНОЕ ОБРАЗОВАТЕЛЬНОЕ федерального университета

УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

Дата подписания: 12.09.2023 15:26:32 УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ Уникальный программный ключ: «СЕВЕРО-КАВКАЗСКИЙ ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ»

d74ce93cd40e39275c3ba2f58486412a1c8ef96f

<del>Пятигорский институт (</del>филиал) СКФУ

## Методические указания

по выполнению лабораторных работ по дисциплине «Аппаратные средства вычислительной техники» для студентов направления подготовки /специальности 10.03.01 Информационная безопасность шифр и наименование направления подготовки/ специальности

(ЭЛЕКТРОННЫЙ ДОКУМЕНТ)

| -                    |       | • •  |   |          | кафедры | информацион |

|----------------------|-------|------|---|----------|---------|-------------|

| безопасности<br>№ от | , сис |      |   | протокол |         |             |

| № от                 |       | 2021 | - |          |         |             |

## Содержание

Лабораторная работа 1. Изучение логических элементов. Основы алгебры логики.

Лабораторная работа 2. Комбинации логических элементов.

Лабораторная работа 3. Построение счетчика двоичных импульсов.

Лабораторная работа 4. Элементы памяти. Триггеры, резисторы.

Лабораторная работа 5. Построение дешифратора сигналов.

## Введение

Данное учебное пособие содержит курс лабораторных работ по дисциплине «Аппаратные средства вычислительной техники» направленный на изучение принципов функционирования и элементной базы вычислительных систем.

Содержащиеся в данном пособии сведения теории, методические указания и рекомендации по выполнению лабораторных работ позволяют использовать его в качестве дополнительного пособия для закрепления курса лекций.

#### ЛАБОРАТОРНАЯ РАБОТА №1

#### Изучение логических элементов. Основы алгебры логики.

**ЦЕЛЬ РАБОТЫ:** Ознакомление с основными характеристиками логических элементов и основами синтеза логических схем. Изучить логические элементы и их переходные характеристики.

#### Компетенции:

| Код    | Формулировка:                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОПК- 4 | способностью понимать значение информации в развитии современного общества, применять информационные технологии для поиска и обработки информации;                                 |

| ПК-1   | способностью выполнять работы по установке, настройке и обслуживанию программных, программно – аппаратных (в том числе криптографических) и технических средств защиты информации; |

## Теоретическая часть.

Математическая логика является частью формальной логики и служит теоретической основой построения электронных вычислительных машин и цифровых устройств. Наиболее широкое применение из области математической логики получила алгебра логики. Базой алгебры логики являются понятия о высказывании, истинности и ложности высказывания, связях между высказываниями. Высказывание или логический аргумент в зависимости от значения бывают истинными или ложными. Значение высказывания может изменяться с изменением обстоятельств, и таким образом высказывание меняет оценку своей истинности. С точки зрения логики, высказывания можно разделить на:

- высказывание истинно постоянно (математически их принимают равными 1);

- высказывание ложно постоянно (математически их принимают равными 0);

- высказывание, которое может быть истинным или ложным в зависимости от определенных условий, т. е. принимать значение 1 или 0 попеременно.

По смыслу высказывания бывают простые и сложные. Простое высказывание – логический аргумент (переменная) – входит в состав сложного высказывания логической функции, которая зависит от истинности или ложности аргумента. Обычно простое высказывание обозначается малыми буквами латинского или русского алфавита: x, e, m, z, m, p, a, b. Сложные высказывания или логические функции, обозначают большими буквами латинского или русского алфавита: A, F, P, X, Y, S, Q. Связи между высказываниями-аргументами по своей логике разные, и из-за этого значение сложного высказывания непостоянное.

Разные комбинации значений входных переменных в логических функциях называются наборами. Функция является полностью заданной, если указаны ее значения для всех наборов значений входных переменных. Сопоставляя каждому набору значение функции, равное 0 или 1, можно получить табличное задание данной функции, которое называется таблицей истинности или таблицей соответствия.

- 1. **Буфер** не изменяет логического состояния цифрового сигнала, т.е. логическая 1 или 0 на входе, вызывается логической 1 или 0 на выходе. Их применяют для повышения нагрузочной способности по току, а так же для формирования логических уровней, действующих в определенном интерфейсе.

- 2. Инвертор осуществляет дополнение логического состояния, т.е. логическая 1 на

входе вызывает 0 на выходе, и наоборот.

- 3. Элемент "И" на выходе этого элемента логическая 1 появляется, только если все входы данного элемента находится в состоянии логической единицы. Все остальные комбинации приводят к появлению логического нуля на выходе.

- 4. Элемент "HE-И" -- на выходе образуется логический 0, когда на всех входах одновременно логическая 1, (другие комбинации вызывают логич. 0).

- 5. Элемент "ИЛИ" -- на выходе появляется 1, если хотя бы один из выходов находится в состоянии 1.

- 6. Элемент "НЕ-ИЛИ" -- на выходе появляется логическая 1, когда на всех входах логический 0.

- 7. Элемент "Исключающее ИЛИ" или сумматор по модулю 2.

В таблице 1 показаны логические функции и их обозначение.

Таблица - Логические функции и их обозначение.

| Таолица - Логиче   | ские функции и их обоз           | начение.                       |                               |

|--------------------|----------------------------------|--------------------------------|-------------------------------|

| Логическая функция | Обозначение по                   | Обозначение по                 | Таблица                       |

| 17                 | стандарту MN/ANST                | стандарту R33939               | истинности                    |

| Буфер              | X Y                              | X Y                            | x y 0 0 1 1                   |

| Инвертор           | $X \longrightarrow \overline{Y}$ | X Y                            | x y 0 1 1 0                   |

| И; А*В=Ү           | A Y                              | A & Y                          | A B Y 0 0 0 0 1 0 1 0 0 1 1 1 |

| НЕ-И; А*В=у        | A<br>B Y                         | A & Y                          | A B Y O O 1 O 1 1 1 O 1 1 1 O |

| ИЛИ; А+В=у         | <u>A</u> <u>Y</u> <u>B</u>       | <u>A</u><br><u>B</u> ≥1        | A B Y O O O O 1 1 1 O 1 1 1 1 |

| НЕ-ИЛИ; А*В=у      | <u>A</u> <u>Y</u> <u>B</u>       | $\frac{A}{B} \geq 1$           | A B Y 0 0 1 0 1 0 1 0 0 1 1 0 |

| Исключающее ИЛИ    | <u>A</u> <u>B</u> <u>T</u>       | $\frac{A}{B}$ =1 $\frac{Y}{A}$ | A B Y 0 0 0 0 1 1 1 0 1 1 1 0 |

#### Оборудование и материалы

Для выполнения лабораторной работы предусмотрены компьютерные классы, находящиеся в аудиториях, оснащенных ПК, а также системное программное обеспечение – OC MS Windows 7 и приложения Office (Excel Word, Access и т.п.).

#### Указания по технике безопасности

Лабораторная работа проводится на ПЭВМ. Запрещается прикасаться к задней панели системного блока при включенном питании, переключать разъемы интерфейсных кабелей периферийных устройств, загромождать верхние панели устройств бумагами и посторонними предметами, допускать попадание влаги на поверхность системного блока, монитора, клавиатуры и других устройств.

## Порядок выполнения работы

Задание 1. Построение переходных характеристик.

Используя оболочку Місто-Сар 8 построить схемы на логических элементах и генераторах цифровых сигналов для анализа их характеристик. Построение переходных характеристик в оболочке Місто-Сар 8 осуществляем следующим образом:

- 1. Создаем новую форму для работы;

- 2. Вставляем необходимые логические элементы, генераторы цифровых сигналов;

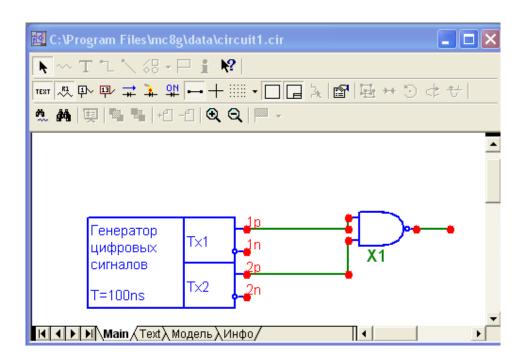

- 3. Соединяем логические элементы с генератором (рис.1)

Рисунок 1-Соединение логических элементов с генератором

- 4. В меню «анализ» выбираем опцию «исследование переходных процессов»;

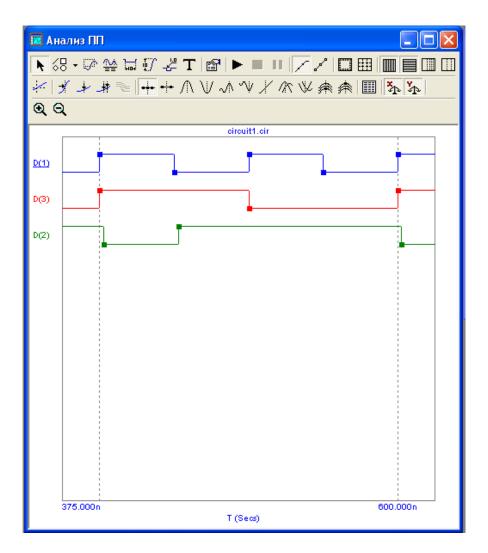

- 5. Выбираем элемент и необходимые выводы на нем для построения графиков переходных процессов (рис.2). Провести анализ переходных характеристик логических элементов.

Рисунок 2 - Графики переходных процессов

**Задание 2.** В оболочке Micro-Cap 8 построить схемы с использованием генераторов цифровых сигналов (синхроимпульсов) и логических элементов: НЕ (инвертор), И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Используя встроенные средства в оболочке Micro-Cap 8 построить графики переходных процессов на входах и выходах каждого логического элемента;

#### Содержание отчета

- 1. Тема

- 2. Цель работы

- 3. Краткое описание выполненной работы.

- 4. Продемонстрировать данную работу на ПК, в соответствии с заданиями, оформить в программной оболочке Microsoft Word.

- 5. Сделать схемы с логическими элементами; графики переходных процессов на входах и выходах логических элементов.

- 6. Сформулировать заключение и выводы

- 7. Ответить на контрольные вопросы.

#### Контрольные вопросы

- 1. С чем связан фазовый сдвиг сигнала на выходе логических элементов относительно входных сигналов?

- 2. Для каких целей необходим буфер?

- 3. Для каких целей необходим инвертор?

- 4. Каким образом преобразует сигналы логический элемент «И»?

- 5. Каким образом преобразует сигналы логический элемент «НЕ-И»?

- 6. Каким образом преобразует сигналы логический элемент «ИЛИ»?

- 7. Каким образом преобразует сигналы логический элемент «НЕ-ИЛИ»?

#### Основная литература

- 1. Айдинян, А.Р. Аппаратные средства вычислительной техники : учебник / А.Р. Айдинян. М. ; Берлин : Директ-Медиа, 2016. 125 с. : ил., схем., табл. Библиогр. в кн. ISBN 978-5-4475-8443-6 ; То же [Электронный ресурс]. URL: //biblioclub.ru/index.php?page=book&id=443412

- 2. Привалов, И. М. Основы аппаратного и программного обеспечения : учеб.-метод. пособие / И.М. Привалов ; Сев.-Кав. федер. ун-т. Ставрополь : СКФУ, 2015. 145 с. 144 с.

- 3. Калачев А.В. Аппаратные и программные решения для беспроводных сенсорных сетей [Электронный ресурс] / А.В. Калачев. 2-е изд. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 240 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/73661.html

## Дополнительная литература

- 1 Ключев А.О. Аппаратные средства информационно-управляющих систем [Электронный ресурс] : учебное пособие / А.О. Ключев, П.В. Кустарев, А.Е. Платунов. Электрон. текстовые данные. СПб. : Университет ИТМО, 2015. 65 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/65791.html">http://www.iprbookshop.ru/65791.html</a>

- 2. Лошаков С. Периферийные устройства вычислительной техники [Электронный ресурс] / С. Лошаков. Электрон. текстовые данные. М. : Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 419 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/62822.html">http://www.iprbookshop.ru/62822.html</a>

- 3. Жуков А.Е. Системы блочного шифрования [Электронный ресурс]: учебное пособие по курсу «Криптографические методы защиты информации»/ Жуков А.Е.-Электрон. текстовые данные.— М.: Московский государственный технический университет имени Н.Э. Баумана, 2013.— 80 c.— Режим доступа: http://www.iprbookshop.ru/31633.— ЭБС «IPRbooks», по паролю

- 4. Функциональные узлы аппаратных средств вычислительной техники [Электронный ресурс] : практикум по дисциплине Аппаратные средства вычислительной техники / . Электрон. текстовые данные. М. : Московский технический университет связи и информатики, 2014. 44 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/61729.html

## Интернет-ресурсы:

- 1. http://www.biblioclub.ru/ электронная библиотека

- 2. http://www.uts-edu.ru/ «Электронные курсы»

## ЛАБОРАТОРНАЯ РАБОТА №2

#### Комбинации логических элементов.

**Цель работы:** Изучить комбинации логических элементов и их переходные характеристики.

#### Компетенции:

| Код    | Формулировка:                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОПК- 4 | способностью понимать значение информации в развитии современного общества, применять информационные технологии для поиска и обработки информации;                                 |

| ПК-1   | способностью выполнять работы по установке, настройке и обслуживанию программных, программно – аппаратных (в том числе криптографических) и технических средств защиты информации; |

#### Теоретическая часть.

Рассмотрим таблицу истинности (таблица 1).

Таблица 1.- Таблица истинности

| Входы |   |   |   | Выход | Входы |   |   |   | Выход |

|-------|---|---|---|-------|-------|---|---|---|-------|

| D     | С | В | A | Y     | D     | С | В | A | Y     |

| 0     | 0 | 0 | 0 | 0     | 1     | 0 | 0 | 0 | 0     |

| 0     | 0 | 0 | 1 | 0     | 1     | 0 | 0 | 1 | 0     |

| 0     | 0 | 1 | 0 | 0     | 1     | 0 | 1 | 0 | 1*    |

| 0     | 0 | 1 | 1 | 0     | 1     | 0 | 1 | 1 | 0     |

| 0     | 1 | 0 | 0 | 0     | 1     | 1 | 0 | 0 | 0     |

| 0     | 1 | 0 | 1 | 0     | 1     | 1 | 0 | 1 | 0     |

| 0     | 1 | 1 | 0 | 0     | 1     | 1 | 1 | 0 | 0     |

| 0     | 1 | 1 | 1 | 0     | 1     | 1 | 1 | 1 | 0     |

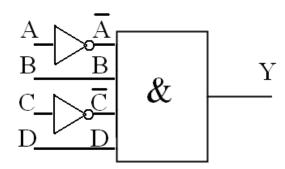

Булева функция для данной таблицы истинности является следующее  $D\overline{C}B\overline{A} = Y$  Логическая схема, построенная на основании этой функции примет вид (рис.1):

Рисунок 1- Логическая схема

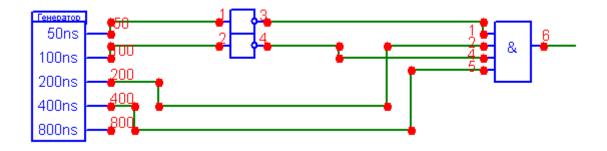

Пример: реализация в Місго-Сар 8, булевой функции:  $Y = \overline{A}\,\overline{B}\,CD$

Рисунок 2- Схема комбинации логических элементов

Рисунок 3- Графики переходных процессов:

## Оборудование и материалы

Для выполнения лабораторной работы предусмотрены компьютерные классы, находящиеся в аудиториях, оснащенных ПК, а также системное программное обеспечение – OC MS Windows 7 и приложения Office (Excel Word, Access и т.п.).

## Указания по технике безопасности

Лабораторная работа проводится на ПЭВМ. Запрещается прикасаться к задней панели системного блока при включенном питании, переключать разъемы интерфейсных кабелей периферийных устройств, загромождать верхние панели устройств бумагами и

посторонними предметами, допускать попадание влаги на поверхность системного блока, монитора, клавиатуры и других устройств.

## Порядок выполнения работы

#### Задание 1.

- 1. Используя оболочку Місго-Сар 8 построить схемы на основе комбинаций логических элементов.

- 2. Провести анализ переходных характеристик комбинаций логических элементов;

- 3. В приведенных ниже таблицах (табл. 2 3) истинности логические уровни выходов (Y) обозначены символами с 1 по 32. Согласно номеру варианта, в таблице 4, выбираются соответствующие значения логических уровней на выходе (Y).

Таблица 2.

| Входы |   |   |   | Выход | Входы |   |   |   | Выход |

|-------|---|---|---|-------|-------|---|---|---|-------|

| D     | C | В | A | Y     | D     | C | В | A | Y     |

| 0     | 0 | 0 | 0 | 1     | 1     | 0 | 0 | 0 | 9     |

| 0     | 0 | 0 | 1 | 2     | 1     | 0 | 0 | 1 | 10    |

| 0     | 0 | 1 | 0 | 3     | 1     | 0 | 1 | 0 | 11    |

| 0     | 0 | 1 | 1 | 4     | 1     | 0 | 1 | 1 | 12    |

| 0     | 1 | 0 | 0 | 5     | 1     | 1 | 0 | 0 | 13    |

| 0     | 1 | 0 | 1 | 6     | 1     | 1 | 0 | 1 | 14    |

| 0     | 1 | 1 | 0 | 7     | 1     | 1 | 1 | 0 | 15    |

| 0     | 1 | 1 | 1 | 8     | 1     | 1 | 1 | 1 | 16    |

Таблица 3.

| Входы |   |   |   | Выход | Входы |   |   |   | Выход |

|-------|---|---|---|-------|-------|---|---|---|-------|

| D     | C | В | A | Y     | D     | C | В | A | Y     |

| 0     | 0 | 0 | 0 | 17    | 1     | 0 | 0 | 0 | 25    |

| 0     | 0 | 0 | 1 | 18    | 1     | 0 | 0 | 1 | 26    |

| 0     | 0 | 1 | 0 | 19    | 1     | 0 | 1 | 0 | 27    |

| 0     | 0 | 1 | 1 | 20    | 1     | 0 | 1 | 1 | 28    |

| 0     | 1 | 0 | 0 | 21    | 1     | 1 | 0 | 0 | 29    |

| 0     | 1 | 0 | 1 | 22    | 1     | 1 | 0 | 1 | 30    |

| 0     | 1 | 1 | 0 | 23    | 1     | 1 | 1 | 0 | 31    |

| 0     | 1 | 1 | 1 | 24    | 1     | 1 | 1 | 1 | 32    |

Таблица 4.

| No | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12        | 13 | 14 | 15        | <i>16</i> |

|----|-----------|----|----|----|----|----|----|----|----|----|----|-----------|----|----|-----------|-----------|

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0  | 1         | 1         |

| 1  | 17        | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28        | 29 | 30 | 31        | 32        |

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1         | 0  | 1  | 0         | 1         |

| No | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | <i>12</i> | 13 | 14 | 15        | 16        |

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 1  | 0         | 1         |

| 2  | <i>17</i> | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28        | 29 | 30 | 31        | 32        |

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0         | 1  | 0  | 1         | 0         |

| №  | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12        | 13 | 14 | <i>15</i> | <i>16</i> |

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 1  | 0  | 0         | 1         |

| 3  | 17        | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28        | 29 | 30 | 31        | 32        |

|    | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1         | 0  | 0  | 1         | 0         |

| NC-         | 1       | 1       | 2        | 1       | -       | (       | 7       | 0       | 0       | 10        | 11      | 12       | 12      | 11      | 15          | 1/          |

|-------------|---------|---------|----------|---------|---------|---------|---------|---------|---------|-----------|---------|----------|---------|---------|-------------|-------------|

| №           | 1       | 0       | 0        | 0       | 5       | 6       | 7       | 8       | 9       | 10        | 0       | 12       | 13      | 14      | 15          | <b>16</b>   |

| 4           | 0       | 18      | 19       | _       |         | 0       | 0       |         | 0       | 1         |         | 0        | 0       | 1       | 0           |             |

| 4           | 17      |         |          | 20      | 21      | 22      | 23      | 24      | 25      | <b>26</b> | 27      | 28       | 29      | 30      | 31          | <b>32</b> 0 |

| Mo          | 0       | 0       | 0        | 0       | 0       | 0       | 1       | 0       | 0       |           | 1       | 0        | 0       | 1       | 0           |             |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

| _           | 0       | 0       | 0        | 1       | 0       | 0       | 0       | 0       | 1       | 0         | 0       | 0        | 0       | 0       | 1           | 0           |

| 5           | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

| NC-         | 0<br>1  | 0 2     | <u>0</u> | 0<br>4  | 5       | 0<br>6  | 1<br>7  | 0<br>8  | 0<br>9  | 1<br>10   | 0<br>11 | 0<br>12  | 0       | 0       | 1<br>15     | 0           |

| №           |         |         | 1        |         |         |         |         |         |         |           | 1       | <u> </u> | 13      | 14      |             | <b>16</b> 0 |

| 6           | 0<br>17 | 0<br>18 | 0<br>19  | 0<br>20 | 0<br>21 | 0<br>22 | 0<br>23 | 1<br>24 | 0<br>25 | 0<br>26   | 1<br>27 | 0<br>28  | 0<br>29 | 0<br>30 | 0           |             |

| 6           | 0       | 0       | 1        | 0       | 0       | 0       | 0       | 0       | 1       | 0         | 0       | 0        | 1       | 0       | <b>31</b> 0 | <b>32</b> 0 |

| Mo          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          |             |

| No          | 0       | 0       | 0        | 0       | 0       | 0       | 0       | 0       | 1       | 0         | 0       | 0        | 0       | 1       | 0           | <b>16</b> 0 |

| 7           | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

| '           | 1       | + -     | 0        | 1       | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| <u>№</u>    | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

| J1 <u>⊻</u> | 0       | 0       | 0        | 0       | 0       | 0       | 0       | 0       | 0       | 1         | 1       | 0        | 0       | 0       | 0           | 1           |

| 8           | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 0       | 0       | 1        | 0       | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 1        | 0       | 1       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

| 31_         | 0       | 1       | 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 1       | 0           | 0           |

| 9           | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 0       | 0       | 0        | 0       | 0       | 0       | 1       | 1       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 1           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

|             | 0       | 0       | 0        | 0       | 0       | 1       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 1       | 0           | 0           |

| 10          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 1       | 0       | 0        | 1       | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 1        | 0       | 0       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

|             | 0       | 0       | 0        | 0       | 0       | 1       | 0       | 0       | 0       | 1         | 0       | 0        | 0       | 0       | 0           | 1           |

| 11          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 1       | 1       | 0        | 0       | 1       | 0       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

|             | 0       | 0       | 0        | 1       | 0       | 1       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| 12          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 0       | 0       | 0        | 0       | 0       | 0       | 0       | 1       | 1       | 1         | 0       | 0        | 0       | 0       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

|             | 0       | 0       | 0        | 0       | 0       | 0       | 1       | 1       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| 13          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

|             | 1       | 0       | 0        | 0       | 0       | 0       | 1       | 0       | 0       | 0         | 1       | 0        | 0       | 0       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | <i>16</i>   |

|             | 0       | 0       | 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0         | 0       | 1        | 1       | 0       | 0           | 0           |

| 14          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

| 10          | 0       | 1       | 1        | 0       | 1       | 0       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| No          | 1       | 2       | 3        | 4       | 5       | 6       | 7       | 8       | 9       | 10        | 11      | 12       | 13      | 14      | 15          | 16          |

| 1.5         | 0       | 0       | 0        | 1       | 1       | 0       | 0       | 0       | 0       | 0         | 0       | 0        | 0       | 0       | 0           | 0           |

| 15          | 17      | 18      | 19       | 20      | 21      | 22      | 23      | 24      | 25      | 26        | 27      | 28       | 29      | 30      | 31          | 32          |

| <u></u>     | 0       | 0       | 0        | 0       | 0       | 0       | 0       | 1       | 0       | 1         | 0       | 0        | 0       | 0       | 0           | 1           |

| No                  | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 16                  | 1         | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|                     | 17        | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|                     | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| №                   | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| 17                  | 0         | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|                     | <i>17</i> | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|                     | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  |

| $N_{\underline{0}}$ | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| 18                  | 1         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

|                     | <i>17</i> | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|                     | 1         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  |

| $N_{\underline{0}}$ | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|                     | 0         | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 19                  | <i>17</i> | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|                     | 0         | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| №                   | 1         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|                     | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 20                  | <i>17</i> | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|                     | 1         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  |

#### Содержание отчета

- 1. Тема

- 2. Цель работы

- 3. Краткое описание выполненной работы.

- 4. Продемонстрировать данную работу на ПК, в соответствии с заданиями, оформить в программной оболочке Microsoft Word.

- 5. Схемы с комбинациями логических элементов; графики переходных процессов на входах и выходах комбинаций логических элементов.

- 6. Таблицы истинности и соответствующие им булевы функции.

- 7. Сформулировать заключение и выводы.

- 8. Ответить на контрольные вопросы.

## Контрольные вопросы

- 1. Для каких целей используются комбинации логических элементов?

- 2. Поясните, каким образом реализуется та или иная булева функция.

- 3. Переведите десятичное число, указанное преподавателем в двоичную форму и осуществите проверку.

#### Основная литература

- 1. Айдинян, А.Р. Аппаратные средства вычислительной техники : учебник / А.Р. Айдинян. М. ; Берлин : Директ-Медиа, 2016. 125 с. : ил., схем., табл. Библиогр. в кн. ISBN 978-5-4475-8443-6 ; То же [Электронный ресурс]. URL: //biblioclub.ru/index.php?page=book&id=443412

- 2. Привалов, И. М. Основы аппаратного и программного обеспечения : учеб.-метод. пособие / И.М. Привалов ; Сев.-Кав. федер. ун-т. Ставрополь : СКФУ, 2015. 145 с. 144 с.

- 3. Калачев А.В. Аппаратные и программные решения для беспроводных сенсорных сетей [Электронный ресурс] / А.В. Калачев. 2-е изд. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 240 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/73661.html">http://www.iprbookshop.ru/73661.html</a>

## Дополнительная литература

- 1 Ключев А.О. Аппаратные средства информационно-управляющих систем [Электронный ресурс] : учебное пособие / А.О. Ключев, П.В. Кустарев, А.Е. Платунов. Электрон. текстовые данные. СПб. : Университет ИТМО, 2015. 65 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/65791.html

- 2. Лошаков С. Периферийные устройства вычислительной техники [Электронный ресурс] / С. Лошаков. Электрон. текстовые данные. М. : Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 419 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/62822.html">http://www.iprbookshop.ru/62822.html</a>

- 3. Жуков А.Е. Системы блочного шифрования [Электронный ресурс]: учебное пособие по курсу «Криптографические методы защиты информации»/ Жуков А.Е.— Электрон. текстовые данные.— М.: Московский государственный технический университет имени Н.Э. Баумана, 2013.— 80 с.— Режим доступа: http://www.iprbookshop.ru/31633.— ЭБС «IPRbooks», по паролю

- 4. Функциональные узлы аппаратных средств вычислительной техники [Электронный ресурс] : практикум по дисциплине Аппаратные средства вычислительной техники / . Электрон. текстовые данные. М. : Московский технический университет связи и информатики, 2014. 44 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/61729.html

#### Интернет-ресурсы:

- 1. <a href="http://www.biblioclub.ru/">http://www.biblioclub.ru/</a> электронная библиотека

- 3. <a href="http://www.uts-edu.ru/">http://www.uts-edu.ru/</a> «Электронные курсы»

#### ЛАБОРАТОРНАЯ РАБОТА 3

#### Построение счетчика двоичных импульсов

**ЦЕЛЬ РАБОТЫ:** Изучить принципы построения счетчиков импульсов. **Компетенции:**

| Код    | Формулировка:                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОПК- 4 | способностью понимать значение информации в развитии современного общества, применять информационные технологии для поиска и обработки информации;                                 |

| ПК-1   | способностью выполнять работы по установке, настройке и обслуживанию программных, программно – аппаратных (в том числе криптографических) и технических средств защиты информации; |

#### Теоретическая часть.

#### Построение счетчика импульсов

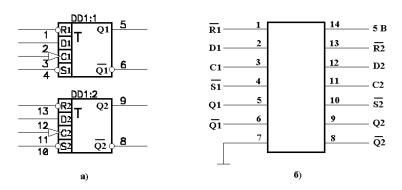

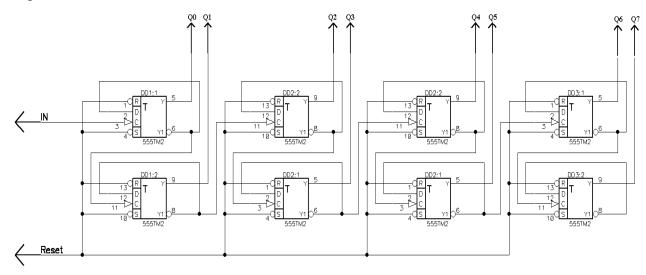

Счетчик импульсов можно построить на микросхемах K555TM2 (см. рис. 4.1), Микросхемы K555TM2 содержат два независимых Д-триггера, имеющих общую цепь питания. У каждого триггера есть выводы D, ^S и ^R, а также комплиментарные выводы Q и ^Q.

Входы  $^{\circ}$ S и  $^{\circ}$ R — асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе; активный уровень для них — низкий. Сигнал от входа D передается на выходы Q и  $^{\circ}$ Q по положительному перепаду импульса на тактовом входе C (от H к B). Чтобы триггер переключился правильно (т.е. согласно таблице 1) уровень на входе D следует зафиксировать заранее, перед приходом тактового перепада.

Таблица 1- Переключения триггера

|                        |    | Bx |   | Выход |   |    |

|------------------------|----|----|---|-------|---|----|

| Режим работы           | ^S | ^R | С | D     | Q | ^Q |

| Асинхронная установка  | Н  | В  | X | X     | В | Н  |

| Асинхронный сброс      | В  | Н  | X | X     | Н | В  |

| Неопределенность       | Н  | Н  | X | X     | В | В  |

| Загрузка 1 (установка) | В  | В  | I | В     | В | Н  |

| Загрузка 0 (сброс)     | В  | В  | I | Н     | Н | В  |

На рисунке 1 представлена микросхема К555ТМ2: а) функциональное графическое обозначение; б) цоколевка.

Защитный интервал должен превышать время задержки распространения сигнала в триггере. Если на входы  $^{\circ}$ S и  $^{\circ}$ Rтриггеров TM2 одновременно подаются напряжения низкого уровня, состояние выходов Q и  $^{\circ}$ Q окажется неопределенным. Загрузить в триггер входные уровни B или H (т.е. 1 или 0) можно, если на входы  $^{\circ}$ S и  $^{\circ}$ R подать напряжение высокого уровня.

Рисунок 1- Микросхема К555TM2: а) функциональное графическое обозначение; б) цоколевка.

Защитный интервал должен превышать время задержки распространения сигнала в триггере. Если на входы  $^{\circ}$ S и  $^{\circ}$ Rтриггеров TM2 одновременно подаются напряжения низкого уровня, состояние выходов Q и  $^{\circ}$ Q окажется неопределенным. Загрузить в триггер входные уровни В или H (т.е. 1 или 0) можно, если на входы  $^{\circ}$ S и  $^{\circ}$ R подать напряжение высокого уровня.

Асинхронная установка нужного сочетания уровней на выходах получится, когда на входы  $^{\circ}$ S и  $^{\circ}$ R поданы взаимно противоположные логические сигналы. В это время входы C и D отключены. Функциональное обозначение триггеров показано на рис. (а), цоколевка на рис. 2.

Рисунок 2- Функциональная схема счетчика импульсов.

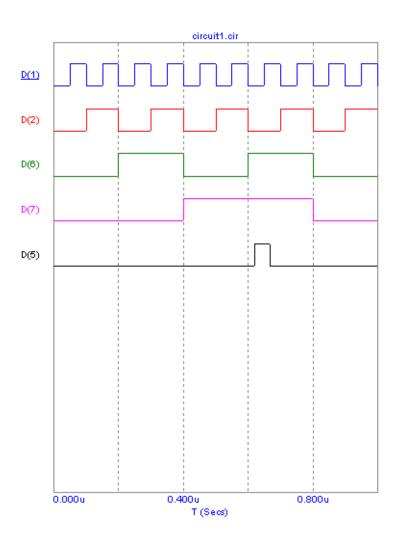

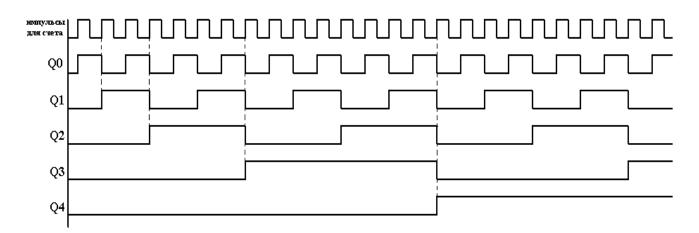

На рисунке 3 показаны циклы работы счетчика. На рисунке 3приведены следующие обозначения: IN — вход счетчика, Reset — сброс счета, Q0 — Q7 включительно — выходы счетчика, где Q0 — 0-ой разряд, а Q7 — 7ой разряд. Циклы работы счетчика показаны на рис. 3

Рис. 4.3. Циклы работы счетчика

## Оборудование и материалы

Для выполнения лабораторной работы предусмотрены компьютерные классы, находящиеся в аудиториях, оснащенных ПК, а также системное программное обеспечение – OC MS Windows 7 и приложения Office (Excel Word, Access и т.п.).

#### Указания по технике безопасности

Лабораторная работа проводится на ПЭВМ. Запрещается прикасаться к задней панели системного блока при включенном питании, переключать разъемы интерфейсных кабелей периферийных устройств, загромождать верхние панели устройств бумагами и посторонними предметами, допускать попадание влаги на поверхность системного блока, монитора, клавиатуры и других устройств.

#### Порядок выполнения работы

#### Задание 1.

Используя оболочку Місто-Сар 8 построить схему счетчика двоичных импульсов на основе генераторов синхроимпульсов и логических элементов;

#### Задание 2.

Построить временные диаграммы сигналов на входе и выходах счетчика импульсов.

#### Задание 3.

Провести анализ их переходных характеристик.

#### Содержание отчета

- 1. Тема

- 2. Цель работы

- 3. Краткое описание выполненной работы.

- 4. Продемонстрировать данную работу на ПК, в соответствии с заданиями, оформить в программной оболочке Microsoft Word.

- 5. Построить временные диаграммы сигналов на входе и выходах счетчика импульсов на логических элементах и провести анализ их переходных характеристик.

- 6.Сформулировать заключение и выводы

- 7. Ответить на контрольные вопросы.

#### Контрольные вопросы

- 1. Каким образом функционирует счетчик двоичных импульсов?

- 2. Функциональная схема счетчика импульсов.

- 3. Циклы работы счетчика.

#### Основная литература

- 1. Айдинян, А.Р. Аппаратные средства вычислительной техники : учебник / А.Р. Айдинян. М. ; Берлин : Директ-Медиа, 2016. 125 с. : ил., схем., табл. Библиогр. в кн. ISBN 978-5-4475-8443-6 ; То же [Электронный ресурс]. URL: //biblioclub.ru/index.php?page=book&id=443412

- 2. Привалов, И. М. Основы аппаратного и программного обеспечения : учеб.-метод. пособие / И.М. Привалов ; Сев.-Кав. федер. ун-т. Ставрополь : СКФУ, 2015. 145 с. 144 с.

- 3. Калачев А.В. Аппаратные и программные решения для беспроводных сенсорных сетей [Электронный ресурс] / А.В. Калачев. 2-е изд. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 240 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/73661.html

## Дополнительная литература

- 1 Ключев А.О. Аппаратные средства информационно-управляющих систем [Электронный ресурс] : учебное пособие / А.О. Ключев, П.В. Кустарев, А.Е. Платунов. Электрон. текстовые данные. СПб. : Университет ИТМО, 2015. 65 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/65791.html">http://www.iprbookshop.ru/65791.html</a>

- 2. Лошаков С. Периферийные устройства вычислительной техники [Электронный ресурс] / С. Лошаков. Электрон. текстовые данные. М. : Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 419 с. 2227-8397. Режим доступа: <a href="http://www.iprbookshop.ru/62822.html">http://www.iprbookshop.ru/62822.html</a>

- 3. Жуков А.Е. Системы блочного шифрования [Электронный ресурс]: учебное пособие по курсу «Криптографические методы защиты информации»/ Жуков А.Е. данные.— М.: Московский государственный технический Электрон. текстовые университет Н.Э. Баумана, 2013.— Режим имени c. доступа: http://www.iprbookshop.ru/31633.— ЭБС «IPRbooks», по паролю

- 4. Функциональные узлы аппаратных средств вычислительной техники [Электронный ресурс] : практикум по дисциплине Аппаратные средства вычислительной техники / . Электрон. текстовые данные. М. : Московский технический университет связи и информатики, 2014. 44 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/61729.html

## Интернет-ресурсы:

- 1. <a href="http://www.biblioclub.ru/">http://www.biblioclub.ru/</a> электронная библиотека

- 2. http://www.uts-edu.ru/ «Электронные курсы»

## ЛАБОРАТОРНАЯ РАБОТА №4 Элементы памяти. Триггеры, регистры.

**ЦЕЛЬ РАБОТЫ:** Изучить принципы работы элементов памяти – триггеров и регистров.

#### Компетенции:

| Код    | Формулировка:                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОПК- 4 | способностью понимать значение информации в развитии современного общества, применять информационные технологии для поиска и обработки информации;                                 |

| ПК-1   | способностью выполнять работы по установке, настройке и обслуживанию программных, программно – аппаратных (в том числе криптографических) и технических средств защиты информации; |

#### Теоретическая часть.

## Триггеры.

Триггерами называют устройства, обладающие двумя состояниями устойчивого равновесия и способные под воздействием внешнего управляющего сигнала скачком переходить из одного устойчивого состояния в другое.

Триггеры выполняют как на отдельных (дискретных) элементах, так и методами интегральной технологии. Их широко используют в различных устройствах, в которых они выполняют функции переключающих, счетных, пороговых и запоминающих элементов. Они составляют 20-40% оборудования ЭВМ.

Несмотря на то, что в настоящее время триггеры на дискретных схемах выполняют редко, физические процессы удобнее рассмотреть на таких схемах. На практике наиболее часто встречаются схемы с коллекторно-базовыми связями (симметричные) и с эмиттерной связью (несимметричные). В качестве активного элемента используют биполярные и полевые транзисторы, туннельные диоды.

Триггеры являются электронным элементом памяти с двумя устойчивыми состояниями, таким образом, триггер позволяет заполнить один из двоичных разрядов. Переход из одного устойчивого состояния происходит под действием внешнего сигнала.

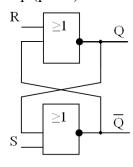

Рассмотрим асинхронный RS триггер (рис.1).

Рисунок 1- Асинхронный RS триггер

Если на вход S подана логическая единица, а на вход R логический ноль, то на выходах получим следующее:

1)

$$\overline{Q} = S + Q = 1 + 0 = 0$$

2)

$$Q=R+\overline{Q}=0+0=1$$

При S=0 и R=1, состояние выходов изменяется следующим образом:  $\overline{Q}$  = 1; Q = 0 При подаче на оба входа логической единицы состояние триггера не определено.

Разрешающее время и быстродействие триггера.

Наименьший интервал времени между запускающими импульсами, вызывающими бесперебойное переключение импульса, называют разрешающим временем  $T_{pas}$ . Величина, обратная разрешающему времени, называется быстродействием триггера ( $\Gamma$ ц):

$$F_{\rm B}=\frac{1}{T_{\rm pas}}.$$

Быстродействие триггера определяет наибольшее возможное число бесперебойных переключений триггера в 1 при неизменном интервале  $T_{pa3}$  между запускающими импульсами и достигает значений порядка 100~MFц. Эффективность многих электронных устройств зависит от быстродействия триггеров. На быстродействие триггера влияет скорость переключения транзисторов, работающих в схеме в ключевом режиме. Для повышения быстродействия используют высокочастотные транзисторы, ключи в ненасыщенном режиме (для устранения задержки выключения, которая связана с процессом рассасывания неосновных носителей в базе насыщенного транзистора). Кроме того, применяют специальные меры, уменьшающие время установления напряжения на коллекторах транзисторов и ускоряющих конденсаторах.

## Регистры.

Регистрами называют устройства, предназначенные для приема, хранения и передачи информации. Последняя в регистре хранится в виде двоичного кода, каждому разряду которого соответствует свой элемент памяти (разряд регистра), выполненный на основе триггеров RS-, JK-, или D-типа.

Регистры классифицируются по следующим видам

- накопительные (регистры памяти, хранения);

- сдвигающие.

В свою очередь сдвигающие регистры делятся:

- по способу ввода-вывода информации на:

- параллельные,

- последовательные,

- комбинированные;

- по направлению передачи информации на:

- однонаправленные,

- реверсивные.

Классификацию регистров можно провести по различным признакам, важнейшими из которых являются способ ввода-вывода информации и характер представления вводимой и выводимой информации.

По способу ввода-вывода информации различают параллельные, последовательные и параллельно-последовательные регистры. В регистрах памяти и ввод информации и ее вывод осуществляются в параллельном коде. При этом время ввода (вывода) всего числа равно времени ввода (вывода) одного разряда. В регистрах сдвига число вводится и выводится последовательно разряд за разрядом. Время ввода (вывода) тразрядного двоичного числа в таких регистрах определяется величиной тс, где Тс- период следования тактовых импульсов, осуществляющих ввод (вывод) информации. В параллельно-последовательном регистре ввод числа может осуществляться в параллельном коде, а вывод - в последовательном или наоборот.

По характеру представления вводимой и выводимой информации различают регистры однофазного и парафазного типов. В однофазных регистрах информация вводится в прямом либо в обратном кодах, а в парафазных - одновременно и в прямом и в обратном. Регистры первого типа строятся на основе D-триггеров, второго - на основе RS-или JK-триггеров. Вывод информации из регистров обоих типов может осуществляться в прямом и в обратном кодах.

Регистры — узлы вычислительной машины, предназначенные для запоминания и временного хранения числа на определенное количество разрядов вправо и влево.

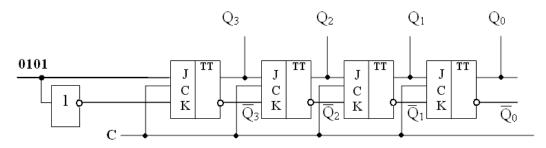

Регистр — это совокупность триггеров, число которых соответствует количеству двоичных разрядов в слове. В последнем четырехразрядном регистре на ЈК триггерах, код двоичного числа, потребует 0101, начиная с младшего, поступает на вход. При поступлении на вход единицы. На выходе Q3 после окончания тактового импульса появится единица (рис.2).

Одновременно со следующим тактовым импульсом на вход поступает нулевое значение нулевого разряда числа.

Рисунок 2- Схема сдвигающего регистра

Таким образом, одновременно с записью значения второго разряда в первом слева триггере, записанное в нем ранее значение первого разряда числа перемещается (сдвигается) в следующий триггер. После третьего тактового импульса происходит третий сдвиг информации вправо.

В параллельном регистре запись числа осуществляет параллельным кодом. Код второго поступает на несколько (по количеству разрядов) входов.

#### Оборудование и материалы

Для выполнения лабораторной работы предусмотрены компьютерные классы, находящиеся в аудиториях, оснащенных ПК, а также системное программное обеспечение – OC MS Windows 7 и приложения Office (Excel Word, Access и т.п.).

#### Указания по технике безопасности

Лабораторная работа проводится на ПЭВМ. Запрещается прикасаться к задней панели системного блока при включенном питании, переключать разъемы интерфейсных кабелей периферийных устройств, загромождать верхние панели устройств бумагами и посторонними предметами, допускать попадание влаги на поверхность системного блока, монитора, клавиатуры и других устройств.

## Порядок выполнения работы

#### Задание 1.

Используя оболочку Місго-Сар 8 построить схемы на основе генераторов синхроимпульсов и триггеров;

Провести анализ их переходных характеристик и сделать выводы.

#### Задание 2.

В оболочке Місто-Сар:

- 1. построить схему триггера на логических элементах и построить графики переходных процессов на входах и выходах триггера;

- 2. построить несколько схем регистров сдвига на триггерах (количество разрядов регистров указывает преподаватель) и построить графики переходных процессов на входах и выходах регистра;

#### Содержание отчета

- 1. Тема

- 2. Цель работы

- 3. Краткое описание выполненной работы.

- 4. Продемонстрировать данную работу на ПК, в соответствии с заданиями, оформить в программной оболочке Microsoft Word.

- 5. Схема триггера на логических элементах и графики переходных процессов на входах и выходах триггера;

- 6. Схемы регистров сдвига и графики переходных процессов на входах и выходах регистров;

- 7. Сформулировать заключение и выводы

- 8. Ответить на контрольные вопросы.

## Контрольные вопросы

- 1. Какие устройства называются триггерами?

- 2. Разрешающее время и быстродействие триггера.

- 3. Дайте определение регистру.

- 4. Для каких целей используются регистры?

- 5. Какие виды регистров Вы знаете?

- 6. Классификация регистров

## Основная литература

- 1. Айдинян, А.Р. Аппаратные средства вычислительной техники: учебник / А.Р. Айдинян. М.; Берлин : Директ-Медиа, 2016. 125 с. : ил., схем., табл. Библиогр. в кн. ISBN 978-5-4475-8443-6; То же [Электронный ресурс]. URL: //biblioclub.ru/index.php?page=book&id=443412

- 2. Привалов, И. М. Основы аппаратного и программного обеспечения : учеб.-метод. пособие / И.М. Привалов; Сев.-Кав. федер. ун-т. Ставрополь: СКФУ, 2015. 145 с. 144 с.

- 3. Калачев А.В. Аппаратные и программные решения для беспроводных сенсорных сетей [Электронный ресурс] / А.В. Калачев. 2-е изд. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 240 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/73661.html

#### Дополнительная литература

- 1 Ключев А.О. Аппаратные средства информационно-управляющих систем [Электронный ресурс] : учебное пособие / А.О. Ключев, П.В. Кустарев, А.Е. Платунов. Электрон. текстовые данные. СПб.: Университет ИТМО, 2015. 65 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/65791.html

- 2. Лошаков С. Периферийные устройства вычислительной техники [Электронный ресурс] / С. Лошаков. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 419 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/62822.html

- 3. Жуков А.Е. Системы блочного шифрования [Электронный ресурс]: учебное пособие по курсу «Криптографические методы защиты информации»/ Жуков А.Е.— Электрон. текстовые данные.— М.: Московский государственный технический университет имени Н.Э. Баумана, 2013.— 80 с.— Режим доступа: http://www.iprbookshop.ru/31633.— ЭБС «IPRbooks», по паролю

- 4. Функциональные узлы аппаратных средств вычислительной техники [Электронный ресурс] : практикум по дисциплине Аппаратные средства вычислительной техники /. Электрон. текстовые данные. М.: Московский технический университет связи и информатики, 2014. 44 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/61729.html

#### Интернет-ресурсы:

- 1. http://www.biblioclub.ru/ электронная библиотека

- 2.http://www.uts-edu.ru/ «Электронные курсы»

# **ЛАБОРАТОРНАЯ РАБОТА 5 Построение дешифратора сигналов**

ЦЕЛЬ РАБОТЫ: Изучить принципы построения дешифраторов сигналов.

#### Компетенции:

| Код    | Формулировка:                                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОПК- 4 | способностью понимать значение информации в развитии современного общества, применять информационные технологии для поиска и обработки информации;                                 |

| ПК-1   | способностью выполнять работы по установке, настройке и обслуживанию программных, программно – аппаратных (в том числе криптографических) и технических средств защиты информации; |

#### Теоретическая часть.

#### 1. Буферирование сигналов магистрали

Буферирование магистральных сигналов применяется для электрического согласования и выполняет две основные функции: электрическая развязка (для всех сигналов) и передача сигналов в нужном направлении (только двунаправленных сигналов). Это первая и наиболее очевидная функция любого УС. Для буферирования наиболее часто используют микросхемы магистральных приемников, передатчиков, приемопередатчиков, нередко называемые драйверами и буферами.

Электрическая развязка подразумевает обеспечение нужных входных и выходных токов (уровни напряжения на ISA –ТТЛ). Входные каскады УС должны обеспечивать уровень входного тока не более 0,8 мА, а выходные и двунаправленные каскады должны выдавать выходной ток не менее 24 мА (при нулевом выходном сигнале). Несоблюдение этого правила может привести к сбоям в работе компьютера и даже к выходу из строя его отдельных узлов. Для предотвращения сбоев и поломок нужно осуществить правильный подбор микросхем.

2. Характеристики микросхем применяемых для буферирования

Приемники магистральных сигналов должны удовлетворять двум основным требованиям: малые входные токи и высокое быстродействие (они должны отрабатывать в течение отведенных им временных интервалов циклов обмена).

Конкретное значение допустимых времён задержек определяется используемой схемой интерфейсной части УС в целом, но при этом микросхемы обычных (не быстродействующих) КМОП серий здесь не годятся, не смотря на их малые входные токи. Не подходят и микросхемы серии К155 (SN74) из-за их больших входных токов.

Требованиям, предъявляемым к приемникам, удовлетворяют следующие серии микросхем: KP1533 (SN74ALS), K555 (SN74LS) и KP1554 (74AC). Величины входных токов логического нуля для них составляют соответственно 0,2 мА, 0,4 мА и 0,2 мА, а величины временных задержек не превышают соответственно 15 нс, 20 нс и 10 нс. Требованиям, предъявляемым к приемникам, удовлетворяют также микросхемы электрически программируемых ППЗУ и ПЛМ серии KP556 (I36, N82S, DM87S HM76).

Требования к передатчикам: большой выходной ток и высокое быстродействие. Часто они должны иметь отключаемый выход (например, для шины данных), т.е. иметь выход с открытым коллектором или с тремя состояниями. Это связано с необходимостью перехода УС в пассивное состояние в случае отсутствия обращения к нему. В качестве микросхем передатчиков можно использовать следующие серии: К155, К555, КР1533, К559 и т.д.

Требования к приемопередатчикам. Они включают в себя требования к приемникам и передатчикам, т.е. малый входной ток, высокое быстродействие и обязательное отключение выходов. В качестве приемопередатчиков используются следующие серии микросхем: КР559ИПЗ (DS8641), КР531АП2, К589АП16 (I8216), КР580ВА86 (I8286), КР1533АП6 (SN74ALS245), К555АП6, КР559ИП13 (DP8307).

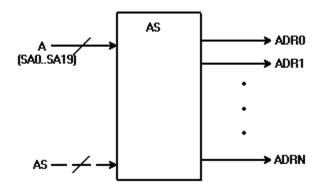

#### 3. Построение селектора адреса

Второй основной интерфейсной функцией, выполняемой УС, работающим в режиме программного обмена, является селектирование или дешифрация адреса. Эту функцию выполняет узел, называемый селектором адреса, который должен вырабатывать сигналы, соответствующие выставлению на шине адреса магистрали кода адреса, принадлежащего данному УС. Обобщенная схема селектора адреса для УС, работающего как устройство ввода/вывода, показана на рисунке 1. Здесь шина А – это шина адреса магистрали, шина АЅ –внутренняя шина УС, на которой присутствует код, сравниваемый с адресом магистрали (может отсутствовать), ADR –выходные сигналы селектора адреса, формируемые при обращении по магистрали к данному УС.

Следует отметить, что совсем не обязательно дешифровать все линии адресной шины магистрали. Часто для упрощения схемы УС удобно часть этих линий отбросить, не заводить на селектор адреса. При этом важно, чтобы адреса проектируемого УС не перекрывались с адресами, занятыми другими устройствами компьютера.

Рисунок 1- Структура селектора адреса

Требования, предъявляемые к селекторам адреса:

- •высокое быстродействие (селектор адреса должен иметь задержку не более чем интервал между выставлением адреса и началом сигнала строба обмена);

- возможность изменения селектируемых адресов (особенно важно для устройства ввода/вывода из-за малого количества свободных адресов);

- малые аппаратурные затраты.

Самое простое решение при построении селектора адреса – использование только микросхем логических элементов.

Основным достоинством такого подхода является высокое быстродействие.

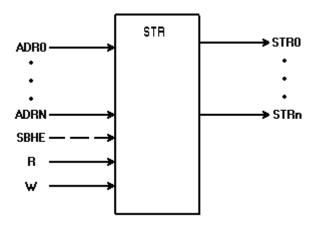

4. Выработка внутренних стробирующих сигналов

Следующая важная функция интерфейсной части УС — выработка стробирующих сигналов синхронно с магистральными командами сигналами (-IOR, -IOW) в случае обращения по адресам УС. Условно узел, выполняющий эту функцию, может быть представлен в следующем виде. На его вход подаются сигналы ADR0...ADRN с выхода селектора адреса, SBHE (в случае необходимости разделения 8- и 16-разрядных циклов), а также буферированные магистральные стробы записи и чтения (R и W). Выходы — это сигналы STR0...STRn, соответствующие обращениям с записью или чтением по всем адресам или группам адресов УС (рис. 2).

Рисунок 2-Структура блока выработки внутренних стробов.

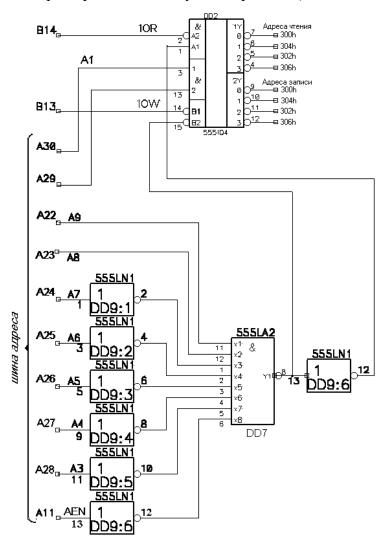

Так как имеется необходимость выработки большого числа внутренних стробирующих сигналов, удобно использовать микросхемы дешифраторов (для селектора адреса, с выработкой внутренних стробов, показанного на рисунке 3 есть возможность использования 4-х адресов при обращении к модулю сопряжения).

Рисунок 3-Дешифратор сигналов ISA.

Возможно построение селектора адреса только на микросхемах дешифраторов, но объём аппаратуры получается при этом очень большим. Поэтому более правильным

решением будет обработка старших адресных разрядов с помощью логических элементов, а младшие – с помощью одной микросхемы дешифратора.

#### Оборудование и материалы

Для выполнения лабораторной работы предусмотрены компьютерные классы, находящиеся в аудиториях, оснащенных ПК, а также системное программное обеспечение – OC MS Windows 7 и приложения Office (Excel Word, Access и т.п.).

#### Указания по технике безопасности

Лабораторная работа проводится на ПЭВМ. Запрещается прикасаться к задней панели системного блока при включенном питании, переключать разъемы интерфейсных кабелей периферийных устройств, загромождать верхние панели устройств бумагами и посторонними предметами, допускать попадание влаги на поверхность системного блока, монитора, клавиатуры и других устройств.

## Порядок выполнения работы

#### Задание 1.

Используя оболочку Micro-Cap 8 построить схему дешифратора сигналов на основе генераторов синхроимпульсов и логических элементов работающих при строго определенных сигналах (управляющих и адресных) на входах.

#### Задание 2.

Построить диаграммы сигналов на входах и выходах логических элементов.

#### Задание 3.

Провести анализ их переходных характеристик и сделать выводы.

## Содержание отчета

- 1. Тема

- 2. Цель работы

- 3. Краткое описание выполненной работы.

- 4. Продемонстрировать данную работу на ПК, в соответствии с заданиями, оформить в программной оболочке Microsoft Word.

- 5. Схема дешифратора сигналов на логических элементах и графики переходных процессов на его входах и выходах;

- 6. Сформулировать заключение и выводы

- 7. Ответить на контрольные вопросы.

#### Контрольные вопросы

- 1. Для каких целей необходим дешифратор мультиплексор?

- 2. Какие требования предъявляют к селекторам адреса?

- 3. В чем заключается буферирование магистральных сигналов?

- 4. Какие требования предъявляются к приемопередатчикам?

- 5. Для каких целей нужна электрическая развязка?

#### Основная литература

- 1. Айдинян, А.Р. Аппаратные средства вычислительной техники: учебник / А.Р. Айдинян. М.; Берлин: Директ-Медиа, 2016. 125 с.: ил., схем., табл. Библиогр. в кн. ISBN 978-5-4475-8443-6; То же [Электронный ресурс]. URL: //biblioclub.ru/index.php?page=book&id=443412

- 2. Привалов, И. М. Основы аппаратного и программного обеспечения : учеб.-метод. пособие / И.М. Привалов; Сев.-Кав. федер. ун-т. Ставрополь: СКФУ, 2015. 145 с. 144 с.

- 3. Калачев А.В. Аппаратные и программные решения для беспроводных сенсорных сетей [Электронный ресурс] / А.В. Калачев. 2-е изд. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 240 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/73661.html

#### Дополнительная литература

- 1 Ключев А.О. Аппаратные средства информационно-управляющих систем [Электронный ресурс]: учебное пособие / А.О. Ключев, П.В. Кустарев, А.Е. Платунов. Электрон. текстовые данные. СПб.: Университет ИТМО, 2015. 65 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/65791.html

- 2. Лошаков С. Периферийные устройства вычислительной техники [Электронный ресурс] / С. Лошаков. Электрон. текстовые данные. М.: Интернет-Университет Информационных Технологий (ИНТУИТ), 2016. 419 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/62822.html

- 3. Жуков А.Е. Системы блочного шифрования [Электронный ресурс]: учебное пособие по курсу «Криптографические методы защиты информации»/ Жуков А.Е.— Электрон. текстовые данные.— М.: Московский государственный технический университет имени Н.Э. Баумана, 2013.— 80 с.— Режим доступа: http://www.iprbookshop.ru/31633.— ЭБС «IPRbooks», по паролю

- 4. Функциональные узлы аппаратных средств вычислительной техники [Электронный ресурс] : практикум по дисциплине Аппаратные средства вычислительной техники /. Электрон. текстовые данные. М.: Московский технический университет связи и информатики, 2014. 44 с. 2227-8397. Режим доступа: http://www.iprbookshop.ru/61729.html

## Интернет-ресурсы:

- 1. http://www.biblioclub.ru/ электронная библиотека

- 2.http://www.uts-edu.ru/ «Электронные курсы»